CISC architecture

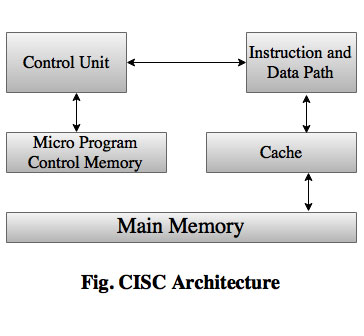

The CISC stands for complex instruction set computer. It is read only memory (ROM) based processor architecture which are designed with a full set of instruction that were intended to provide needed capabilities in the most efficient way. Basically, the CISC processor architecture is designed to simplify compilers and to improve performance under constraints such as small and slow memories. This processor is easy to program and make efficient use of memory. CISC processor has variable length instructions where the length often varies according to the addressing mode hence instructions require multiple clock cycles to execute. It is easy for micro-coding new instructions which allow designers to make CISC processor upwardly compatible means a new processor could run the same programs as earlier processors because the new processor would contain a superset of the instructions of the earlier processors. In CISC architecture which has software control unit consists of micro programmed control memory. The fig of CISC architecture given in below, the fig shows the CISC architecture with micro programmed control memory and unified cache.

Most CISC architectures have a complex instruction-decoding logic for a single instruction to support multiple addressing modes. Common characteristics of most CISC hardware architecture are a small number of general purpose registers result in having instructions which can operate directly on memory, flag register also called as condition register, several special purpose registers such as stack pointer, interrupt handling, and so on.